AMD Zen 6 : vers une nouvelle interconnexion plus rapide et économe

AMD abandonnerait le SERDES au profit d’une interconnexion « Sea-of-Wires » dans Zen 6. Objectif : réduire la consommation et améliorer la bande passante entre chiplets.

NEWS

Moins de latence, plus d’efficacité : Zen 6 va passer au “Sea-of-Wires”

AMD prépare un gros changement d’architecture pour ses futurs processeurs Zen 6 ! Depuis Zen 2, la communication entre les chiplets passait par la technologie SERDES, qui convertit les données en flux série pour traverser le package. Mais ce procédé, bien que pratique, consomme pas mal d’énergie et ajoute de la latence.

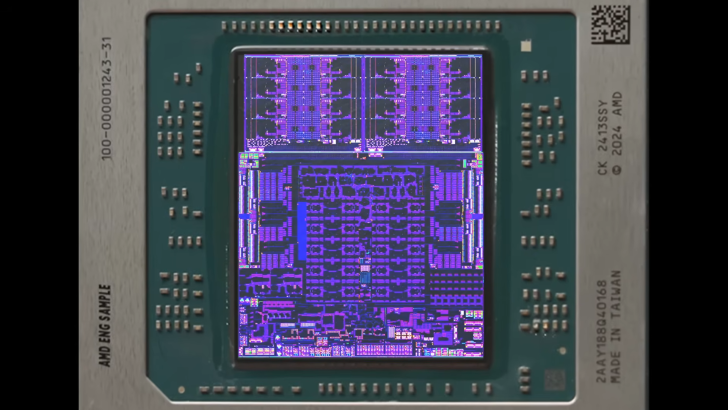

Avec Strix Halo, AMD a commencé à tester une approche différente : au lieu de convertir les données, les dies sont reliés par de fins fils parallèles (un « Sea-of-Wires ») grâce au procédé InFO-oS de TSMC et à une couche de redistribution. En clair, les chiplets communiquent directement via des ports parallèles beaucoup plus larges.

Les avantages sont clairs : moins de consommation, moins de latence, et une bande passante qui peut être augmentée simplement en multipliant les ports. Cela demande des designs plus complexes, mais les gains sont tels qu’AMD devrait reprendre cette approche dans Zen 6.

Ce changement est loin d’être anodin : l’interconnexion D2D est devenue critique dans les processeurs modernes, où CPU, GPU et NPU doivent échanger de plus en plus vite. Avec l’arrivée des fonctions d’IA intégrées et la montée en puissance des puces multichiplet, réduire la latence et améliorer l’efficacité énergétique est un levier aussi important que le gain en puissance brute. En choisissant le « Sea-of-Wires », AMD montre clairement qu’elle prépare Zen 6 pour ces nouveaux usages.

Source : wccftech.com

#AMD #Zen6 #hardware